# Embedded Systems

# **Protecting Firmware**

**Security for Binary Executables**

The GNU Compiler and Linker

More on Paging

A Paean to Noise

Crenshaw's Divine Hammer

**Internet Appliance Design:** Speech Coding Algorithms

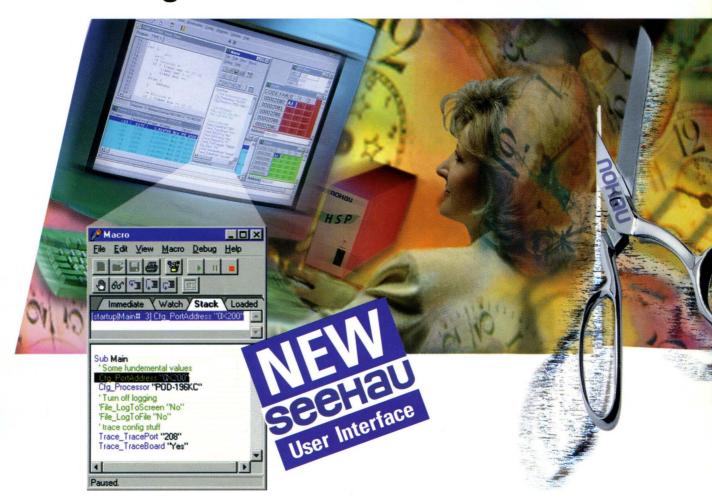

# Cut Development Time

Using In-Circuit Emulators and BDM's

#### **Macros**

- · Macro debug capability

- Project support

- · Command line

- Shadow RAM support

- . Single step in your macro

- GUI capable macros

#### **Key Features**

- Real-time emulation at maximum chip speeds

- · High level support for popular C compilers

- · Advanced tracing capabilities

- · Configurable user interface with remote hookup capability

- High speed connection to PC through parallel port (LPTx) or plug-in ISA card

Nohau Supports These Microcontroller Families 8051 80C196 683xx 68HC11 P51XA ST10 MCS296 MCS251 68HC16 C166 68HC12 M16C

### www.nohau.com

51 East Campbell Avenue, Campbell, CA 95008 Phone: 1-888-88NOHAU (1-888-886-6428) Fax: 408-378-7869 E-mail: sales@nohau.com

visionICE

visionCLICK

visionPROBE

**Embedded Support Tools Corporation**

# contents

FEBRUARY 2000

#### **COVER**

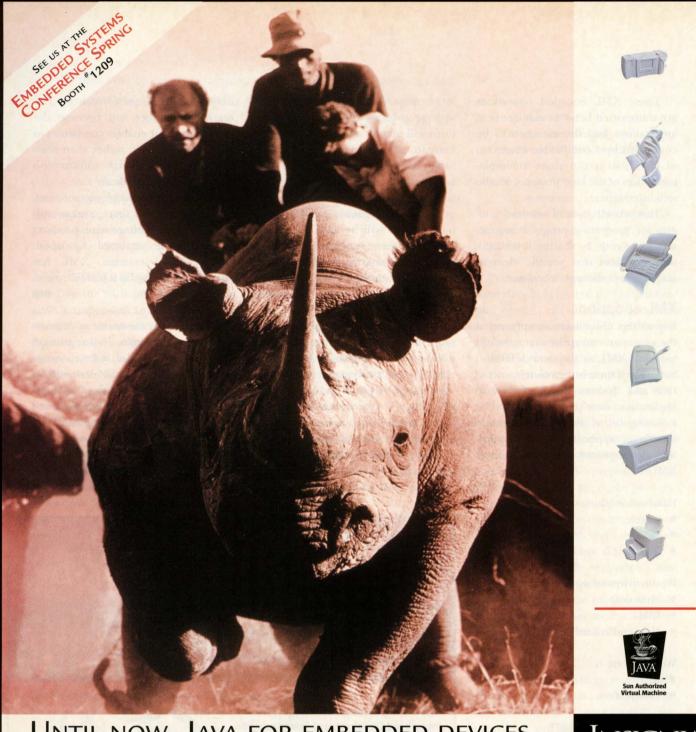

Protecting your binary executables from reverse engineering by competitors isn't a matter to be taken lightly these days.

Cover illustration by Rupert Adley.

#### **Cover Story**

24

#### **Protecting Binary Executables**

Any company that develops embedded products must make a substantial investment of resources to get to the product stage. This article surveys the techniques available for protecting the resulting binary executable from hackers and/or reverse engineering by potential or current competitors.

BY MATT FISHER

### Embedding with GNU: The GNU Compiler and Linker

The GNU compiler, gcc, is capable of producing high-quality code for embedded systems of all types. Here the author discusses the gcc features that are most useful for embedded engineers.

BY BILL GATLIFF

#### **Final Part**

#### Data Memory Paging Management, Part 2

This article, which began last month, explains a method to detect any potential paging errors in assembly programs.

BY HUGH O'BYRNE

80

Detect and find potential paging errors using one programmer's detailed method.

#### **Featured Section**

## internet appliance design

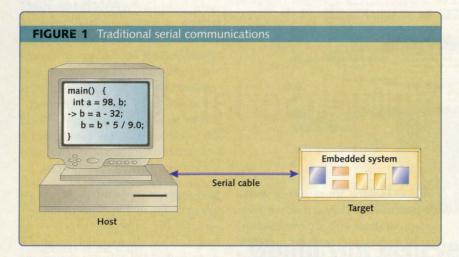

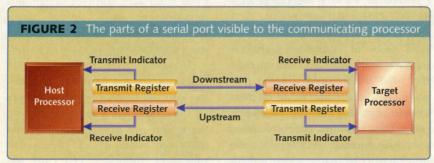

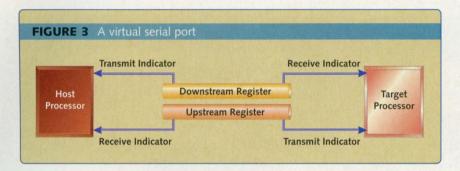

### 33 CONNECTING... Virtual Serial Ports

What if you need a serial port when there are none, or all of them are already being used for other purposes? Here are some tips on creating virtual serial ports from other hardware that you may already have at your disposal.

BY MICHAEL BARR

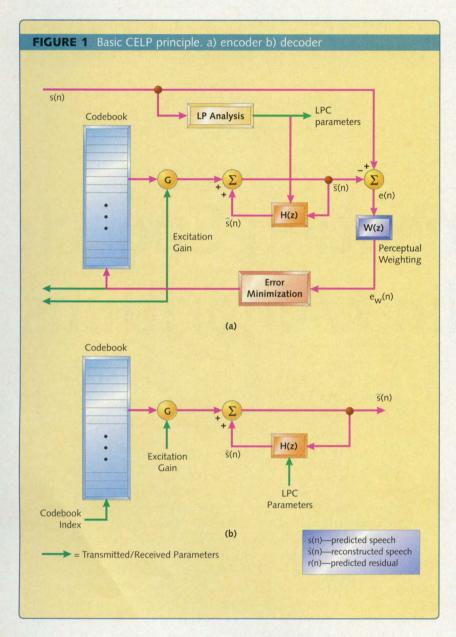

### 39 Implementing Speech Coding Algorithms

This article describes some techniques you can use to implement speech coding standards in a real-time system.

BY DAVID H. CRAWFORD AND EMMANUEL ROY

### 55 Embedding with XML

The eXtensible Markup Language (XML) is more flexible than HTML, which makes it appropriate in embedded systems that use web technologies.

BY SCOTT LAWRENCE

### **61** Embedded Internet Tools

New internet appliance design products.

### columns

7 On Hammers and Nails BY JACK W. CRENSHAW

63 Top-Level cv-Qualifiers in Function Parameters

BY DAN SAKS

95 A Paean to Noise

BY DON MORGAN

113 Reality Bites

BY JACK G. GANSSLE

117 STATE OF THE ART Finding C Level

103

The Rabbit2000 eight-bit micro-processor from Rabbit

### departments

#### 5 #INCLUDE

#### **Beginnings and Endings**

Whether this year marks the end of an era or the beginning of a new one might be debatable, but changes abound regardless.

BY LINDSEY VEREEN

#### **103 NEW PRODUCT GALLERY**

Rhapsody in MicroC from I-Logix; SurroundView from Accelerated Technology; Slim740 ChipConnect from Mitsibushi; DProbeTriCore Level 2 emulator from Hitex Development Tools; more

106 CAREERS

108 MARKETPLACE

112 ADVERTISER INDEX

Explore the mysteries of the Golden Ratio, courtesy of Jack Crenshaw.

### "If only I had spent less time on debug...

If you are developing a Pentium

class target using a reference

design or off-the-shelf board,

please take a moment to speak

with our staff. They will insure your

design is on track, and tool friendly

if debug is needed in the future.

I remember when I budgeted for my project. I refused to spend money on debug tools. I didn't think I would need them. The money I saved would make me a hero.

Now, my project is one month, two months ... six months overdue. Nobody thinks I'm a hero. What would I give to get some of that time back?

Microtek debug tools can make time. They speed up development and testing, saving you precious time at the end of the project, where you need it most!

Microtek emulators offer the debug features you need to track down and correct software, hardware, and system integration issues. They can find the errors software debuggers cannot see.

First, emulators can debug before the operating system is functioning. If an unexpected issue is affecting boot up, an emulator can find it. They are also operational after a hard crash. This is significant, because software debuggers lose debug information. Microtek emulators keep track of the last 128 KB of bus cycles, allowing you to sift through and find the problem.

Additional interfaces: CAD/UL® and Windriver Tornado II®

Finally, if there is a subtle issue during the integration of hardware, Microtek EA emulators are capable of providing a clock-cycle-byclock-cycle trace that allows you to view each signal and determine whether it was in the correct state. Microtek's tools are clearly

superior to software debug solutions.

There has never been a project that couldn't use more time when it's critical ... like in final testing when everything has come together ... or in final debug, when everything is going down in flames.

Wouldn't it be great to deliver your next project on time? Next time, be sure to put a Microtek emulator in your project plan from the start.

It will help take the knot out of your stomach. And it will improve your company's bottom line!

### MICROTEK

1 (800) 886-7333

Phone (503) 533-4463 Fax (503) 533-0956 Email - info@microtekintl.com

Financing Available

### Beginnings and Endings

n the December issue, I remarked that my editorial would be my last of the millennium. A veritable plethora of readers instantly turned on me. One grumbled:

"By now I am resigned to the fact that the general media refer to 2000 as the start of the next century and millennium. However, it is really very sad to see this mistake made in a technical magazine. Can't you do better than this? On the bright side maybe your last article of the millennium will be able to avoid having such a gaff."

Ouch. And that was one of the gentler letters I received. Ten years ago (that is, January 1990) I acknowledged the discrepancy between what was popularly perceived as the beginning of the new decade and what a close analysis of the calendar and a reflection on history would seem to indicate. I observed that for those who acknowledge the least significant bit (LSB) to be zero, then the least significant year (LSY) ought to be zero as well; hence, no problem.

Okay, that argument might have been slightly specious. Nevertheless, this time around, I just yielded to popular thinking and assumed that the millennium began last month. Actually, it would be better if the millennium does begin next year, because the parties will be much less expensive than they were this time around. You couldn't find any venue that didn't soak you for two or three times the normal New Year's rates for the privilege of celebrating the alleged millennium.

Actual millennium or not, a few changes are in store for Embedded Systems Programming this year. As you may know, several months ago Miller Freeman's parent company, United News & Media plc, acquired CMP, the publisher of EETimes. Beginning this month, Embedded Systems Programming will be

published under the CMP brand and will be part of the group that includes EETimes. Integrated System Design, Communication Systems Design, and Electronic Buyers' News. This is a swell match for us. The EEtimes folks et al. are an unbeatable bunch, talented, smart, knowledgeable about the industry, and great writers to boot, and we look forward to significant cross pollination. This union will result in some major changes to our Internet presence as well, as will become evident over the next several months.

Another change I expect to see in the near future is the addition of a West Coast technical editor for Embedded Systems Programming. Michael Barr is doing a bang-up job on the East Coast, and we'd clone him for the San Francisco office if we could. Since that solution is problematical, I'd like to find someone else who's just as good. I guess you'd describe the perfect candidate as a bit of a teacher, a bit of a writer, and a bit of a project manager, with the heart and soul of an engineer. So if you have an inclination to make the leap into the fast-paced, multitasking, and altogether wacky world of publishing, now is your chance. It would be the perfect way either to start the new millennium or to end the old one, depending on your proclivities.

lvereen@mfi.com

#### EDITORIAL DIRECTOR

Vereen, lvereen@mfi.com

#### MANAGING EDITOR

Michael Shapiro, mshapiro@mfi.com

#### TECHNICAL EDITOR

#### SPECIAL PROJECTS EDITOR Tarita Whittingham, twhittingham@mfi.com

ASSISTANT EDITOR

Felisa Yang, fyang@mfi.com

#### CONSULTING TECHNICAL EDITORS

Jack G. Ganssle Jerome L. Krasner, PhD

#### CONTRIBUTING EDITORS

Larry Mittag Don Morgan P.I. Plauge

#### PRESIDENT/ELECTRONICS

#### VICE PRESIDENT/ELECTRONICS

#### EMBEDDED/DSP GROUP DIRECTOR

#### **PUBLISHER**

Eric Berg, (415) 278-5220

#### CALIFORNIA SALES MANAGER

#### CALIFORNIA SALES ASSISTANT Molly Bruns, (415) 278-5298

WESTERN ACCOUNT EXECUTIVE

SALES ASSOCIATE, RECRUITMENT

EASTERN REGIONAL SALES MANAGER

#### Damon Graff, (781) 235-8258

#### PRODUCTION COORDINATOR

#### CIRCULATION MANAGER

CIRCULATION DIRECTOR

#### SUBSCRIPTION CUSTOMER SERVICE

Toll Free: (888) 847-6177 Non-U.S. subscribers: (847) 647-8602 embedded@halldata.com

#### Back issues may be purchased on a pre paid basis through: Miller Freeman, 16 West 23rd St., Suite 200, Lawrence, KS 66046; (800) 444-4881; (785) 841-1631

#### Sherry Bloom, (415) 808-3980

**EXECUTIVE PRODUCER, EMBEDDED.COM**

#### ONLINE PRODUCTION COORDINATOR

#### PRESIDENT/CEO, CMP MEDIA INC.

#### **EXECUTIVE VICE PRESIDENTS**

Regina Starr Ridley John Russell Steve Weitzner Tony Uphoff

#### GLOBAL SALES & MARKETING

SENIOR VICE PRESIDENT/ BUSINESS DEVELOPMENT Pam Watkins

Visit our Web site a www.embedded.com

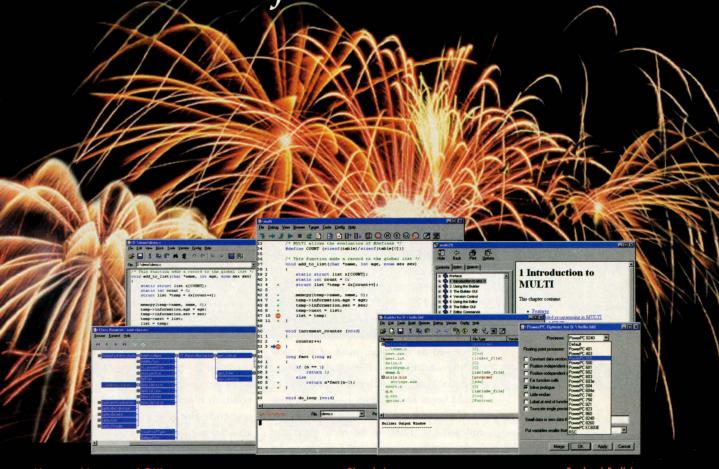

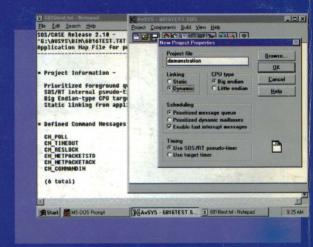

### ULTI 2000

The New IDE for the New Millennium

- New and Improved GUI

- · Graphical Browser

- · On-Line Help

- Syntax Coloring and Auto Indenting

- Simulator

- · Version Control

- C++ Debugging

- EventAnalyzer

- Project Builder

- Code Coverage

- · Run-Time Error Checking

- Profiling

The Best Compilers.

The Best Debuggers.

Now, all wrapped up in a brand new, powerful, easy to use IDE. Once you try MULTI 2000, you won't want to struggle with "old fashioned" tools ever again.

Contact us now for a Free Evaluation CD and

Green Hills

start the millennium with a bang!

# On Hammers and Nails

"To a person whose only tool is a hammer, every problem looks like a nail," goes an old saying. To belabor the obvious, the saying has a negative connotation. The idea is that if you only know how to do things a certain way, you're going to try to use that method for every problem you encounter. Sometimes it will be appropriate. Most times, it won't.

The following story is 100% gospel truth: my father's favorite tool was the hacksaw. I'm not talking about a mild infatuation here; he was head-overheels in *love* with hacksaws, and saw every problem as a new opportunity to put one to work. He once sawed off a stub of water pipe, flush with the concrete floor. When I suggested maybe this wasn't one of his better ideas, he assured me that the pipe was part of the old pump system, and no longer had water pressure in it.

He was wrong.

Our house had those old-fashioned (meaning, in this case, superior to today's) doorknobs that were adjustable for end play. The doorknob on the door to my mother's room had gotten loose, and she asked my father to fix it. He took one look at the doorknob, wiggled it a few times, then turned to me and said, "Son, go fetch my hacksaw."

My mother and I screamed in horror, and I ended up adjusting the knob myself, as well as every subsequent mechanical problem around that house.

Maybe that was his plan all along.

Thinking about it, I realize that the hammer/nail saying would make a pretty good motto for this column.

The column's title is, after all, "Programmer's Toolbox," and my purpose from the get-go has been to provide you readers with as many and as varied a collection of tools as possible. The general idea is that the more tools you have, the more likely you are to have the right one for the job.

In a way, this column is all about craftsmanship. The average homeowner's toolbox has a hammer. The

- Recognizes which tool best fits the problem

- Knows when a new tool is needed

For the record, this concept also applies well to one's choice of programming language. We've all met people who are outspoken advocates of one language or another. You've got your C fanatics, your C++ fanatics, your Visual BASIC fanatics, and, per-

# Optimization should not be like trying to drive a square peg into a round hole with the wrong kind of hammer.

handyman's toolbox may have a claw hammer and a ball-peen hammer. The craftsman's toolbox has those, plus a tack hammer, a rubber mallet, a wooden mallet, several styles of auto body hammer, three sizes of sledgehammer, and so on. You get the idea. Though it takes skill to be a craftsman, it also takes a well-equipped toolbox.

You have to have both the skills and the toolbox. Give my father a handyman's toolbox, and he would use only the hacksaw. On the other hand, Stradivarius could never have made those exquisite violins if his only tool was a bent screwdriver. You have to have both.

A craftsman:

- Has a good collection of tools

- Knows how to use them all

- Knows when and where to use them

haps the most fanatic of all, aficionados of Forth, APL, and other obscure languages. Each claims benefits for his or her favorite language that can't be achieved in any other.

Way back in the dark ages of personal computers, one of the most egregious misuses of a tool came from programmers in Microsoft BASIC. The Microsoft BASIC for the Radio Shack TRS-80 had a feature whereby you could enter assembly-language subroutines, byte by byte, as decimal integers, then execute them. Some TRS-80 programmers prided themselves in writing BASIC programs using hundreds, if not thousands, of bytes of executable "data." Today, some people spend all their time, and even make professional careers out of, writing macros for Microsoft Word and Excel.

Of course, you, dear readers, would

Of all the reasons I can think of for using a given language for a given problem, the worst possible reason has to be: "It's the only one I know."

never fall into this trap. Your toolbox has more than one language in it because, as software craftsmen, you know that each tool has its uses, you know the advantages and disadvantages of each, and you know when and how to use each one. Of all the reasons I can think of for using a given language for a given problem, the worst possible reason has to be: "It's the only one I know."

Lately, however, it's occurred to me that the story about the hammer and the nails has, like the nail itself, another end to it. Lately, it seems that I've been encountering, in both my work and my play, a nail of a particular new shape. And here I stand, with the wrong kind of hammer. I'm talking about optimization.

Lately, I've encountered quite a few problems that seem to involve fitting functions to observed data, for one reason or another. Naturally, we'd like to make the fit as "good" as possible, which usually implies minimizing some kind of error criterion.

Normally, such problems would be a natural for the least-squares fit, also known as "linear regression," or sometimes even "nonlinear regression." However, none of the problems I've been bumping into lately lend themselves very well to least-squares solutions. Although I'm sure there must be other solutions I haven't thought of yet, at least I've been able to see that a good, general-purpose function optimizer can and will pound these newfangled nails into submission. I have a gut feeling that once we have a good set of function optimizers in our respective toolboxes, we'll be seeing a whole new class of nails, where we once saw only thorns. We may even find that they get used as often as my father's proverbial hacksaw.

Hence our current mission to study the techniques for function minimization.

#### The story so far

In the last few months, we've been looking at ways to find the minimum of a function, f(x), of a single variable. We got as far as a method based on searching the function space by halving intervals, when we ran into a question of robustness. That question led me into a digression, last month, to seek a method that behaved itself when the function in question was being coy, and trying to hide from us the true location of the minimum.

Specifically, we worried about situations not often considered in other texts, where two or more samplings of the function yield exactly the same value for f(x). Though we might feel justified in claiming that exactly equal values are extremely unlikely using floating-point arithmetic, I showed you some examples last month, hardly pathological cases, where exactly equal values were not only likely, but almost inevitable.

We spent most of last month addressing this problem, and seeking a way to search the problem space without having an elusive minimum slip from our clutches. I found a solution, which is based on "wiggling" one of the sampling points in an attempt to force the minimum out of hiding. Having done so, we're now ready to proceed with the mainstream process of developing a good, general-purpose tool. Or perhaps a set of them.

#### Where were we?

When we left off last month, we had arrived at a pretty robust method for searching for a minimum of a function:

$$y = f(x) \tag{1}$$

given three starting points which "bracket" the function. By that I mean that we start with three points P<sub>0</sub>, P<sub>2</sub>, and P4 such that:

$$y_2 < y_0 \text{ and } y_2 < y_4$$

(2)

Starting from this configuration guarantees us that there is at least one minimum in the interval  $x_0..x_4$ , and the algorithm is designed to home in on it by reducing the size of that interval without letting the minimum slip away. The method involved halving each interval, testing the value of f(x) at the new points  $P_1$  and  $P_3$ , and choosing three of the five points such that the relation in Equation 2 is maintained. In that way, we inexorably tighten the net around the minimum until it's found within some acceptable epsilon range of x.

(By the way, I apologize for the confusion in naming these points. In last month's article and previously, I've been calling them P<sub>1</sub>..P<sub>5</sub>. The code, however, shows them as Po..P4. We tried to make the change in editing last month, to keep the nomenclature consistent, but we missed the edit deadline. I'll try to be consistent, and use the latter nomenclature from now

I thought you'd like to see the performance of our halving algorithm, for our standard test function:

$$f(x) = \cos(2\pi x^3) \tag{3}$$

The exact value of the minimum is given by:

$$x_{\min} = \sqrt[3]{\frac{1}{2}} = 0.7937005259841 \tag{4}$$

Table 1 shows the five points used at each iteration. The highlighted points,  $x_1$  and  $x_3$ , are the ones generated anew during that iteration. I've chosen to show the values as fractions rather than decimal numbers, so you can best see the bisection process in operation. To see it even better, convert each fraction to the same denominator, and you'll see that the numerators always vary by one, across the row. After nine iterations, we have the minimum bracketed between 203/256

# ONE GIANT LEAP FOR MANKIND. (AND MILLIONS OF LITTLE STEPS FOR THE ENGINEERS)

30 years ago the American Space Program landed a man on the moon for the III first time, and millions watched it happen live. The Infineon Technologies Space Program isn't quite so glamorous – but we do have our mon Today, our development tools partne working together to make the di process for our 8- and 16-Bit Microcon TriCore and DSP products easier for work with and use in your next application. For more information on our tools, turn to the next pages, or visit us on our web site www.spacetools.com

### Hands-on Computer Labs in Embedded Systems Applications, Chips & Tools!

## SIMPLIFY THE DESIGN PROCESS AND GET YOUR BREAKTHRO

This is your chance to the leading embedded and their development evaluate dozens of microcontrollers tool chains-in an actual collect

**EmbeddedSystems**

April 3-7, 2000

Mission College Technology Center Santa Clara, CA.

#### A FULL WEEK OF 2-HOUR TUTORIALS ON THE HOTTEST NEW EMBEDDED APPLICATIONS:

Embedded Internet, Industrial & Motor Control, USB, Communications, Routers, Information and Appliances, and CAN etc.

• WindowsCE Workshops • Panel Discussions on EEMBC, NEXUS, System on a Chip, etc. • Discussions on Trends in Embedded Systems Development by Jerry Krasner • Analysis by Tom Starnes and Jim Turley on the newest microcontroller trends • and more!

AMD 186, Elan, and K6 C166, TriCore Philips 8051, XA ST10 STPC M All Families g Z8 subishi M16C, Slim 740 EC V800. 78K d E5 Configurable SOC s Microconve

> chip PIC 16 la 68HC08, M-Core

Register On-line Today and Receive FREE Evaluation Boards, a Visor Delux or PalmV

www.EmbeddedU.com

### Infineon Technologies 8-, 16-, and 32-Bit Hardware & Software Development Tools Support

### Evaluation + Application Board Starterkit S<sub>T</sub>K16x.500

http://www.lauterbach.com

Digital Input Digital Output Analog Input PWM LCD

LCD Stepper Motor Control Serial Interface (SIO) CAN

10BaseT Ethernet

SAB-C 164CI SAB-C165 SAB80C166 SAB-C167LM SAB-C167CR-LM SAB-C167CS-32FM "Plug & Play" Starterkit

160 x 120 mm EVA-Board

Cable included

Power Supply included

2 \* 16 Character LCD-Display

16 LED for I/O Line Indication

DIP-Switch for Digital Input

A/D Conversion

Stepper Motor Circuit

2 CAN Driver

free Demo Programs with

open C-Code

powerful Download Tools

including TQMinimodul

Fax: (49) 8153-9308-34 • eMail: info@tqc.de • Internet: www.tqc.de

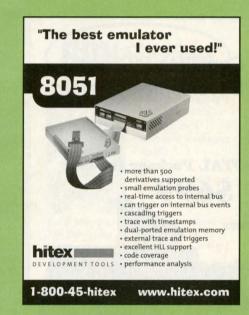

### DProbe 167 In-circuit Emulator

#### Small ...

What is small enough to hold in one hand but has enough functionality to get the job done ... fast! Our DProbe167! Through sophisticated ASIC technology the DProbe167 can go with the developer anywhere easily and functionality is not compromised. The DProbe167 is also upgradeable with its modular design. And even the difficulties of adaptation are made simple with our revolutionary PressOn technology.

These are not the only reasons why we have the most C166 emulators installes around the world. Contact us today and we will tell you more about how the DProbe167 can help you get ahead in today s competitive world.

... but smart!

Hitex Development Tools

710 Lakeway Drive, Suite 280

Sunnyvale, CA94086

Tel: (800) 45HITE

Tel.: (800) 45HITEX

Tel.: (408) 733 7080

Fax: (408) 733 6320

E-mail: info@hitex.com

**hitex**DEVELOPMENT TOOLS

#### I<sup>2</sup>C Bus and SMBus Tools

MCC

MICRO COMPUTER CONTROL

PO Box 275 Hopewell, NJ 08525

Tel: (609) 466-1751 Fax: (609) 466-4116

Email: info@mcc-us.com

www.mcc-us.com

- I<sup>2</sup>C/SMBus Monitors

- **Protocol Analyzers**

- Host Adapters

- Smart Battery Tools

- Keypad-LCD-I/O ICs

- Prototyping Boards

- · Dist. & Mux. Boards

VISIT OUR WEB SITE TO LEARN MORE ...

Detailed information at: www.pOSEK.com © 1999 Integrated Systems, Inc., pOSEK is a registered trademark of Integrated Systems, Inc.

IDE, Compiler, Debugger, Real-time OS & more...

Keil Software develops, manufactures, and distributes software development tools for the 8051, 251, and 166 microcontroller families. Development tools include C compilers, assemblers, real-time kernels, debuggers & simulators, integrated environments, and evaluation boards. Our web site provides up-to-date information about our development tools, evaluation software, updates, application notes, and example programs.

Keil Software, Inc. 16990 Dallas Parkway, Suite 120

Dallas, TX 75248-1903 © 800-348-8051 / 972-735-8052

In Europe and Asia: **Keil Elektronik GmbH** Bretonischer Ring 15 D-85630 Grasbrunn - Munich © ++49 89 456040-0

www.keil.com

Infineon Technologies 8-, 16-, and 32-Bit Hardware & Software Development Tools Support

### EMUL166"-PC

In-Circuit **Emulator** Siemens C166 & C500 Family

ohau's EMUL166-PC supports the Infineon Technologies C166 family of microcontrollers, including C167CR, C167SR, C165, C163, C161RI and their associated Xperipherals. The EMUL166-PC emulator system consists of a card which connects to the PC's printer port (LPTx:), and a pod (containing the controller, memory and logic) and a cable

connecting the two. The pod consists of two PCB boards with the ability to connect to a third board for tracing capabilities. The optional trace board can record and trigger on internal ROM and external buses. External trigger in/out is also

available

EMUL51"-PC

supports the Infineon Technologies C500 family including the C505C, C505CA and C515C.

51 E. Campbell Ave. Campbell, CA 95008-2053 TEL: (408) 866-1820 FAX: (408) 378-7869 E-Mail: sales@nohau.com URL: http://www.nohau.com

#### The Best Compilers • The Best Debuggers

Now, all wrapped up in a brand new, powerful, easy to use IDE. Once you try MULTI 2000, you won't want to struggle with "old fashioned" tools ever again. Contact us now for a Free Evaluation CD and start the millennium with a bang!

US Headquarters: 805.965.6044 European Headquarters: +44 (0)1494 429336 Email: sales@ghs.com · www.ghs.com

### **EMUL166-PC Features:**

- Emulates at maximum chip speed (33MHz) High-level support for all

- popular C-compilers Set hardware and software breakpoints

- 256K to 1M external pod

- Optional trace board

memory available Customizable register windows

• PHYTEC Spectrum CD-ROM including software development tools (C Compiler, Assembler, Debugger and Monitor), example programs, extensive documentation

Stick It In!

www.phytec.com

PHYTEC Messtechnik GmbH

55129 Mainz GERMANY

Tel: +49 (06131) 9221-0

Fax: +49 (06131) 9221-22

Robert-Koch-Str. 39

#### IF IT WEREN'T FOR THE CMX RTOS, WE'D HAVE TO FIND A DIFFERENT USE FOR MICROCONTROLLERS.

Most people agree that microcontrollers without development tools are just worthless chunks of silicon—until you add the CMX-RTX Real-Time

**CMX-RTX Supports Most** 8-, 16-, 32-Bit Processors & DSPs

For Infineon we support:

8051, 80C16x & TriCore

• TCP/IP stack also Available •

680 Worcester Road, Framingham MA 01702 PH: (508) 872-7675 email: cmx@cmx.com FAX: (508) 620-6828

- Phillips: 80C51, 80C51XA, Smart Cards, Contactless Cards Infineon: TriCore, C500 Mitsubishi: M16C, 37700 Motorola: 68HC05, 68HC08,

EUROPEAN DISTRIBUTOR FOR

Member of IEEE-ISTO-5001 (NEXUS) Consortium

ttp://www.ashling.com

Free Demo today!

/isit

and AppNotes

PHYTEC America LLC

Tel: (800) 278-9913

Fax: (206) 780-9135

255 Ericksen Avenue NE

Bainbridge Island, WA 98110

• PHYTEC FlashTools download utility

### Infineon Technologies 8-, 16-, and 32-Bit Hardware & Software Development Tools Support

### TCP/IP FOR C16x

Fast, compact embedded TCP/IP networking solutions for C16x

· to 256 KB SRAM, to 256 KB Flash, seial interfaces · Development Board with AC adapter and DB-9 serial interfaces · Controller User's Manual, QuickStart Manual and schematics

- TCP/IP protocols

- Embedded Web Server

- Internet Access Package

- Supports PHYTEC KitCON and Keil Toolchain

J S SOFTWARE

SNMP

7175 NW Evergreen Pkwy. Suite 100 Hillsboro, OR 97124 TEL: 503-844-6614 • FAX: 503-844-6480 EMAIL: info@ussw.com • www.ussw.com

#### THE DEBUGGER OF CHOICE BY 8051 PROGRAMMERS!

- **Custom support for NOHAU's EMUL51-PC**

- Turbo Debug Power plus Windows ease-of-use

Tel: (905)274-6244 Fax:(905)891-2715 info@chiptools.com

Then chances are you need an adapter for your emulator. We provide Interconnect solutions for any device, any IC package, or any application.

· Fast and accurate tech-support.

· The industry's most experienced design team.

> Need quick turn? How does two weeks sound!

**Emulation Solutions** Phone: 408.855.8527 rw.adapters.com

and 813/1024, which is, in decimal, the range:

0.79296875 .. 0.794921875

The width of this interval is 1/512. or 0.00195. Perhaps more to the point, the middle value is only 0.0002 from the true solution. So far, we have narrowed the width of the range containing the solution to give us only the first two digits, but we're definitely homing in on the solution. Only 11 more iterations should reduce the error to one part in a million, which is about all one can hope for from a function minimizer. You can see, then, that the term "slow" is a relative one. Much faster methods may be out there, but you have to admit, 20 iterations is not an unreasonably large number, especially for such a simple algorithm.

#### **Four-point bisection**

The bisection algorithm isn't perfect, but it certainly does work, especially when I use the tweak I call "wiggling" the new point to resolve ties in the function values. Crude as it is, the possibility of the minimum escaping our grasp is virtually nil. The biggest problem with the method is that we perform two new function evaluations per iteration. That's certainly better than the 10 we had not too many issues ago, but it's exactly twice as many as we

Let's not forget that we can't push any minimization algorithm too far in our quest for a solution. The nature of the problem assures that we can't expect to get six, eight, or even 15 digits of accuracy in the solution. At the limit, as we approach the minimum, every continuous function looks like a parabola, and the closer we get to the solution, the flatter and flatter that parabola gets, until it's indistinguishable from a straight line. At that point, we can't say where the solution lies; we can only say that it must be between x<sub>0</sub> and x<sub>4</sub>. This is not the

As long as we aren't too greedy, we can inexorably close the noose around the minimum until we can be sure we have it corralled tightly enough. The minimum cannot escape our grasp.

most satisfying solution in the world; as computer types, we're used to getting answers back that are accurate to as many digits as the floating-point format allows.

However, in this case, you definitely must get used to disappointment. The nature of the problem simply won't allow you the satisfaction of such accuracy. If our algorithm is robust, as I think this one is, we can guarantee that the minimum we seek will not escape our grasp

is between x<sub>0</sub> and x<sub>4</sub>, and my best guess as to its location is halfway between them." Thus, to this algorithm, it's the reduction in the interval-the tightening of the noosethat is the important thing. Looking at Table 1, it's easy to see how this noose is tightened at every iteration. Because the process is predictable, we can easily estimate how many iterations we'll need to get a satisfactory solution.

Once we recognize that the whole

| TABLE 1 Points used in bisection |         |          |          |          |         |  |  |

|----------------------------------|---------|----------|----------|----------|---------|--|--|

| Iteration                        | x0      | x1       | x2       | х3       | x4      |  |  |

| 0                                | 0       | 1/4      | 1/2      | 3/4      | 1       |  |  |

| 1                                | 1/2     | 5/8      | 3/4      | 7/8      | 1       |  |  |

| 2                                | 3/4     | 13/16    | 7/8      | 15/16    | 1       |  |  |

| 3                                | 3/4     | 25/32    | 13/16    | 27/32    | 7/8     |  |  |

| 4                                | 3/4     | 49/64    | 25/32    | 51/64    | 13/16   |  |  |

| 5                                | 25/32   | 101/128  | 51/64    | 103/128  | 13/16   |  |  |

| 6                                | 101/128 | 203/256  | 51/65    | 205/256  | 103/128 |  |  |

| 7                                | 101/128 | 405/512  | 203/256  | 407/512  | 51/64   |  |  |

| 8                                | 405/512 | 811/1024 | 203/256  | 813/1024 | 407/512 |  |  |

| 9                                | 203/256 |          | 813/1024 |          | 407/512 |  |  |

because of incorrect decisions made in choosing the bracketing points. As long as we aren't too greedy, we can inexorably close the noose around the minimum until we can be sure we have it corralled tightly enough. The minimum cannot escape our grasp. However, we can most definitely squeeze it out, if we try to tighten the noose too much.

Later in this series, we'll look at methods that use quadratic interpolation to give our best guess as to the actual location of the minimum. The bisection method, however, doesn't use such an approach. With this method, we are not so much interested in the location of the minimum itself, as the size of the range x<sub>0</sub>..x<sub>4</sub> that brackets it. At the end of the iteration, we can only say, "The minimum

purpose of the exercise is to bring x<sub>0</sub> and x4 closer together, we should ask ourselves: how many function evaluations will it take to do this at every step? Clearly, the answer is that we can get by with only one. As an added bonus, we are required to maintain only four internal data points, rather than five.

The trick is to recognize that we don't need to compute both x1 and x3 in a single iteration. We can do them on alternate iterations. Note carefully that we must bisect both the left-hand and right-hand intervals. The only way we're going to reduce the bracketing interval, x<sub>0</sub> .. x<sub>4</sub>, is to move both end points inward. But we don't have to do both motions in a single step. We can do them on alternate steps.

The code of Listing 1 does this.

#### LISTING 1 Single bisection

```

/* Perform one step of a minimization by single

* bisection. Input required is three points, of

* which the middle one is strictly smaller.

* The points need not be evenly spaced.

*/

void bisect(double (*f)(double), double &xO, double &yO,

double &x2, double &y2,

double &x4, double &y4,

int count)

double x_mid, y_mid;

// alternate bisection on even and odd values

if(count & 1)

// Bisect the first interval

x \text{ mid} = (x0+x2)/2;

y_mid = f(x_mid);

// if new point is lower,

// use as new middle

if(y_mid < y2)

x4 = x2;

y4 = y2;

x2 = x_mid;

y2 = y_mid;

return;

// if it's higher, move in left limit

if(y_mid > y2)

x0 = x_mid;

y0 = y_mid;

}

else

// Bisect the second interval

x_{mid} = (x2+x4)/2;

y_mid = f(x_mid);

// if new point is lower,

// use as new middle

if(y_mid < y2)

x0 = x2;

y0 = y2;

```

Here, I've used an iteration counter to tell me whether I should bisect the left-hand or the right-hand interval. For simplicity, I've left out my little "wiggle" tweak, but never fear: we'll put it back for the final version.

In Table 2, I've shown how the function converges, in the same format as Table 1. Comparing the two tables, can you see the main difference? We've reduced the rate of convergence. There's no such thing as a free lunch, and by reducing the number of function evaluations, we've also assured that we get less improvement, in terms of reducing the interval, per iteration.

In Table 1, after nine iterations our denominator was 512. In Table 2 it's 64-a factor of eight smaller. Nevertheless, the algorithm of Listing 1 represents an improvement in performance. Before, we needed 18 function evaluations to get a reduction in interval by 2-9. On average, we reduce the interval by a factor of  $\sqrt{2}$ , or 1.414, per function evaluation. The new algorithm needs nine evaluations to get a reduction by 2-6, which means that, on average, we reduce the interval by a factor of 22/3, or 1.588, per function evaluation-definitely an improvement. As we increase the number of iterations, the new algorithm is bound to win, hands down.

#### What about intervals?

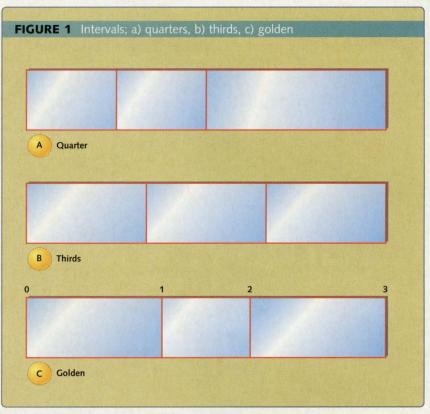

Although the code of Listing 1 works just fine, it leaves us in a peculiar situation with respect to symmetry. When we were using five points, we used bisection to give us four equalwidth intervals. Choosing three of the five points for the next iteration gave us two equal-width intervals again, so the solution maintained a certain symmetry. This is not so when we use only four intervals. The situation is as shown in Figure 1a. After the bisection, we end up with an oddly asymmetric configuration. On the average, we can expect the minimum to lie to the left of the centerline half

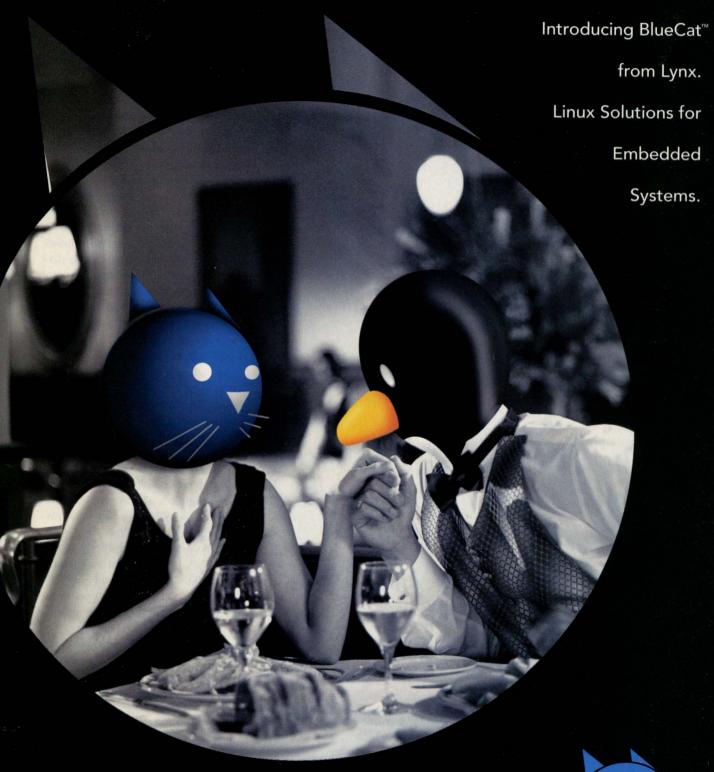

### The Start of Something Big.

www.bluecat.com

Of course, one may always argue that beauty is in the eye of the beholder. Some people might like rooms made like bowling alleys, or square rooms.

```

LISTING 1, continued Single bisection

x2 = x_mid;

y2 = y_mid;

return;

// if it's higher, move in right limit

if(y_mid > y2)

x4 = x_mid;

y4 = y_mid;

3

}

/* Solve for minimum of function, using n successive bisections.

* Initial points _MUST_ represent legal configuration, i.e.,

* y0 > y1, y2 > y1.

* The points need not be evenly spaced.

double minimize(double (*f)(double), double &xO, double &yO,

double &x1, double &y1,

double &x2, double &y2, double eps)

-

// protection from infinite loop

int i = 60;

while((fabs(x2-x0)>eps)&&(i>0))

bisect(f, x0, y0, x1, y1, x2, y2, i);

i-;

cout << "iteration failed" << endl;</pre>

return x1;

```

| TABLE 2         Points used, single bisection |         |         |       |         |         |  |  |

|-----------------------------------------------|---------|---------|-------|---------|---------|--|--|

| teration                                      | x0      | х1      | x2    | х3      | х4      |  |  |

| 0                                             | 0       |         | 1/2   | 3/4     | 1       |  |  |

| 1                                             | 1/2     | 5/8     | 3/4   |         | 1       |  |  |

| 2                                             | 5/8     |         | 3/4   | 7/8     | 1       |  |  |

| 3                                             | 5/8     | 11/16   | 3/4   |         | 7/8     |  |  |

| 4                                             | 11/16   |         | 3/4   | 13/16   | 7/8     |  |  |

| 5                                             | 3/4     | 25/32   | 13/16 |         | 7/8     |  |  |

| 6                                             | 3/4     |         | 25/32 | 51/64   | 13/16   |  |  |

| 7                                             | 25/32   | 101/128 | 51/64 |         | 13/16   |  |  |

| 8                                             | 101/128 |         | 51/64 | 103/128 | 13/16   |  |  |

| 9                                             | 101/128 |         | 51/64 |         | 103/128 |  |  |

the time, so we'll select the two equalwidth intervals for the next iteration. The other half, though, leaves us with one interval twice as large as the other.

Although this situation is hardly fatal-on the next iteration, the wider interval will be halved-it does leave us wondering if we've made the right choice for the divisions.

Since we now are using four points instead of five, the obvious solution is to divide the full interval into thirds, as shown in Figure 1b. But that solution doesn't work, either. After the division, we'll end up selecting only two of the three intervals, which are now equal in width. We're back to a bisected situation, and therefore back where we were in Figure 1a.

So where does this lead us? Figure 1a shows us that we can't always have equal-width intervals. Figure 1b says that even if we try to make them so, we'll soon be back to the same situation.

Given that we can't have the equalwidth intervals that we'd like, can we at least have a division that gives us the same relationship between intervals, at each iteration? Yes, we can, and that's what Figure 1c is all about.

What makes this geometry so special? Well, if you look at the proportions of the two left-hand intervals, you'll see that it is the same as the larger proportion. Stated another way, the ratio of the distances 0..1 and 1..2 is the same as the distances 0..2 and 2..3. The same is true at the right-hand end. In other words, regardless of which pair of intervals we must choose for the next iteration, the intervals will always have the same ratio. What's more, this ratio will continue to hold for all future divisions.

#### **Golden oldies**

You have just met the famous Golden Ratio, sometimes called the Golden Section. It's a world-famous number

whose roots extend back into antiquity. It was certainly known to the ancient Greeks; it appears in much of their architecture. Some folks say it was known to the pyramid builders, as well. It can be found in other Egyptian architecture, too.

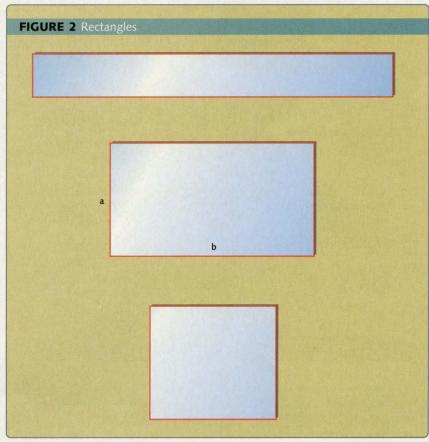

The question regarding the Golden Section was originally posed in architecture this way: given that we're going to build a rectangular room, what proportions would be most pleasing to the eye? Some examples are shown in Figure 2. Clearly a long, skinny rectangle like the first example is not going to work. Aside from the obvious problem that there would be no room for the pool table, it just doesn't look right. Likewise, a square is no good-it's too boring. And a rectangle that's too close to a square would have the same problem. The one in the middle is, as Goldilocks said, "just right."

Of course, one may always argue that beauty is in the eye of the beholder. Some people might like rooms made like bowling alleys, or square rooms. But it's been asserted down through the ages that most people prefer a room shaped like the middle rectangle. That room has the property that the ratio of the two sides, a/b, is the same as the larger side to the total. In other words,

$$\frac{a}{b} = \frac{b}{a+b} \tag{5}$$

Now, this one equation won't give us enough information to solve for both a and b; that would be like allowing only one sized room. We can, however, solve for the ratio, by letting x =b/a. Some manipulation gives:

$$\frac{1}{x} = \frac{x}{1+x}$$

or  $x^2 - x - 1 = 0$  (6)

This is a quadratic equation, and has roots:

# **FUJITSU**

### HITACHI

& Italtel

NEC 0

3Com

Some of the biggest names in the business come to us for smart networking solutions.

We're glad to chip in.

THE HEART OF SMART™

If you get excited just thinking about the possibilities for networking and computing, you're our kind of designer. And we're happy to connect you with all kinds of smart solutions. DigitalDNA technology from Motorola is more than chips. It's software, systems and the ideas of thousands of innovative engineers dedicated to helping create the next generation of routers, switches, servers, modems, desktops and more. You'll find DigitalDNA in leading-edge technology like 0.10µm copper interconnect CMOS-based solutions. The world's fastest copper interconnect SRAMS. And a wide portfolio of highly scalable PowerPC cores. So whenever you need a smart networking solution, you know the name to turn to. www.digitaldna.motorola.com

POWERPC" • FSRAM • COMMUNICATIONS PROTOCOL MODULES • DSP • LDMOS/RF • COLDFIRE®

#### LISTING 2 Solution by Golden Section

```

/* Perform one step of a minimization using the golden ratio.

* Input required is three points, of

* which the middle one is strictly smaller.

* The points need not be evenly spaced.

void golden(double (*f)(double), double &xO, double &yO,

double &x2, double &y2,

double &x4, double &y4){

{

double x_mid, y_mid;

static const double golden = (sqrt(5)-1)/2;

// Divide the first interval

x_mid = x0 + golden*(x2-x0);

y_mid = f(x_mid);

// if new point is lower,

// use as new middle

if(y_mid < y2)

x4 = x2;

y4 = y2;

x2 = x_mid;

y2 = y_mid;

return;

// if it's higher, move in left limit

if(y_mid > y2)

x0 = x_mid;

y0 = y_mid;

}

/* Solve for minimum of function, using n successive divisions

* based upon the golden section.

* Initial points _MUST_ represent legal configuration, i.e.,

* y0 > y1, y2 > y1.

* The points need not be evenly spaced.

*/

double minimize(double (*f)(double), double &xO, double &yO,

double &x1, double &y1,

double &x2, double &y2, double eps)

double temp;

// protection from infinite loop

int i = 60;

```

$$\frac{1-\sqrt{5}}{2} \text{ and } \frac{1+\sqrt{5}}{2} \tag{7}$$

Since the first root gives a negative number, we'll take the second, and write:

$$x = \frac{1 + \sqrt{5}}{2} = 1.618033989 \tag{8}$$

This number is called the Golden Ratio, and is usually denoted by  $\phi$ . It has some fascinating properties. For example:

$$\phi^2 = \phi + 1$$

$$\frac{1}{\phi} = \phi - 1$$

(9)

The number pops up in all kinds of interesting places. Pick any number at random. Add one to it, and take the reciprocal. Add one to that, and take the reciprocal again. Keep doing that long enough, and you arrive at  $\phi$ . Or, take the ratio of any two successive terms in the Fibonacci series:

#### 1, 1, 2, 3, 5, 8, 13, 21, 34, ...

This ratio also converges to  $\phi$ . The ratio appears in the most surprising places, such as the number of petals on some flowers, or the sizes of the chambers in a seashell. A philosopher might argue that the reason things proportioned according to  $\phi$  is pleasing to our eyes is because the number is fundamental to nature.

So what does all this have to do with finding function minima? Simply that the proportions of Figure 1c also are obtained from the Golden Section. Given the full interval from 0 to 3, the interval from 0 to 2 is given by the ratio  $\phi$ -1. Likewise, the interval from 0 to 1 is gotten by scaling 0..2 by the same ratio.

Imagine we go into the minimumseeking function formerly known as bisect() with the three points 0, 2, and 3. We get the new point, 1, by the formula:

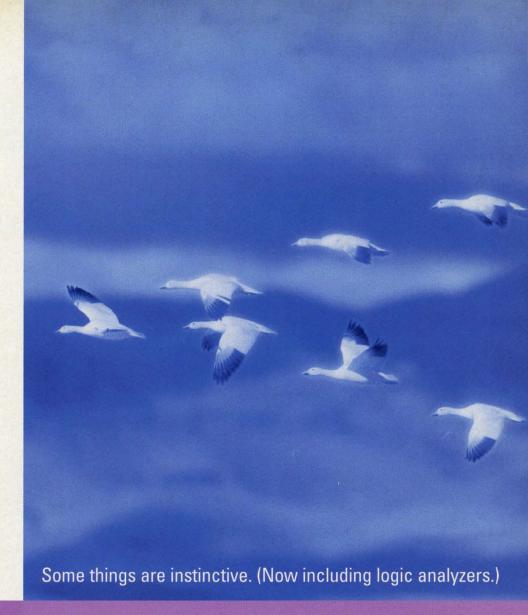

Logic Wave

- Debug designs with 8- and 16- bit microcontrollers

- 100 MHz state analysis and 250 MHz timing analysis

- 128 K memory per channel

- 34 channels of logic analysis

Doing what comes naturally. That's the idea behind Logic *Wave*, Agilent Technologies' new logic analyzer. It may be the easiest logic analyzer you've ever used. How? For starters, it's PC-based, for familiar, simple operation. So you won't need to waste hours learning—and relearning—the interface.

You can draw the trigger easily by selecting a trigger condition from a drop-down menu. And its low cost means you can actually afford one of your own. Because a logic analyzer isn't very helpful if you have to share it with ten other engineers.

Experience Logic *Wave* for yourself. Visit our web site for a FREE download of the actual interface software. Or call us to get a FREE demo on CD-ROM. And talk to another engineer who'll answer your questions about Logic *Wave's* ease of use. Although, after you've used it once, you probably won't have any.

www.agilent.com/find/bi 1-800-452-4844, Ext. 6918

The Real **Embedded** Developer's **Toolkit**

Solutions for microprocessors including: 8051, C166/ST10, M16C, 196, DSP56xxx, 68xxx, PowerPC, TriCore & CARMEL

TASKING Understands the value of your time. You've got to get that product to market yesterday, ahead of schedule - reducing development costs. Time is money.

Call us today at **1-800-458-8276**

visit our web site at: www.tasking.com

However, there's a much cleaner way to accomplish the same thing, and that's to swap points PO and P3 before each computation. The function thinks it's always dividing the left-hand interval, but in fact it's not.

### LISTING 2, continued Solution by Golden Section. while((fabs(x2-x0)>eps)&&(i>0)) golden(f, x0, y0, x1, y1, x2, y2); temp = x0;x0 = x2;x2 = temp;temp = y0; y0 = y2;y2 = temp;i-; cout << "iteration failed" << endl;</pre> return x1;

$$x_1 = x_0 + (\phi - 1)(x_2 - x_0) \tag{10}$$

We can make our program do this with a simple one-line change to the function. Or, rather, a two-line change, since the math appears twice, depending on the value of count. However, we can do better than that. The use of the count parameter has always seemed to me a kludge, anyhow. We had to introduce it to make sure that the function alternated left and right bisections. However, there's a much cleaner way to accomplish the same thing, and that's to swap points P<sub>0</sub> and P<sub>3</sub> before each computation. The function thinks it's always dividing the left-hand interval, but in fact it's not.

It may seem like a waste of clock cycles to keep swapping the data around like this. If this bothers you, feel free to go with the longer form as in Listing 1. However, I suspect that the code to execute the test on count, and to pass its value into the function,

probably costs more than the data swapping. Anyhow, the new code just looks cool, doesn't it?

The modified code is shown in Listing 2. Next month, I'll clean it up a bit more, put back the "wiggle" gimmick, and add a few other niceties.

#### A correction

In the December issue, I gave the incorrect Internet URL for Scilab. The correct URL www-rocq. inria.fr/scilab/scilab.html. Sorry about the mistake. Many thanks to Keith Wright and John B. Williston for straightening me out.

Jack W. Crenshaw a senior principal design engineer at Alliant Tech Systems Inc. in Clearwater, FL. He did much early work in the space program and has developed numerous analysis and real-time programs. He holds a PhD in physics from Auburn University. Crenshaw enjoys contact and can be reached via e-mail at jcrens@earthlink.net.

INTEL CPU PLATFORM

WIDE AREA NETWORKING

SYSTEM PLATFORMS

**DSP TECHNOLOGIES**

### HERE'S A NO-NONSENSE MESSAGE ABOUT OUR TOTAL TELECOM SOLUTION. DON'T BE FOOLED BY ITS SIMPLICITY.

#### Only RadiSys offers the total telecommunications solution.

A solution this complete is hard to pull off. A lot of vendors offer different parts of telecom solutions. Only RadiSys has the vision and technical expertise to deliver the total, integrated solution across both PCI and CompactPCI architectures. RadiSys has acquired Texas Micro, and is now positioned to redefine how the market is buying OEM embedded telecommunications systems. Now you can let us put the total solution together. Download our comprehensive white paper on SS7, and find out how simple it is to get the total solution from one source at www.radisys.com, or call 1-877-837-6859.

State of the art Pentium solutions for Pentium II and Pentium III architectures

Enterprise and carrier class CompactPCI

WIDE AREA NETWORKING Field-proven frame relay, SS7, ATM, T1/E1, X.25, IP and other protocols and interfaces

Advanced TI C6x voice processing solutions-hardware and algorithms

Download FREE white paper today! www.radisys.com/SS7

Any company that develops embedded products must make a substantial investment of resources to get to the product stage. This article surveys the techniques available for protecting the resulting binary executable from hackers and/or reverse engineering by potential or current competitors.

ompanies in the embedded industry usually make substantial investments of time, money, and intellectual resources to solve typical design problems. The result of a successful project is a product in which the company probably has a longer-term financial interest. Protecting embedded software from unwanted reverse engineering by potential competitors or hackers is generally of the utmost importance.

The purpose of this article is to survey some options for protecting binary executables stored in a product's EPROM. This is an introductory, high-level treatment of the subject; additional techniques surely exist that I won't cover in this survey. With this article I intend to foster awareness of the subject and to pique your interest to explore further if your circumstances warrant. The survey of protection techniques follows a brief overview of decompilation.

Following the survey I'll present two scenarios for which some of these techniques may prove worthwhile.

#### Decompilation

Most ESP readers are familiar with the compilation process. Compilation enables programmers to write software in a high-level language, expressing program flow in a way that is closer to how the human mind works-more abstract than what today's microprocessors can handle. The highlevel language/compiler combination reduces the abstraction to a set of specific instructions the microprocessor can understand.

Decompilation, then, is simply the reverse process: taking the low-level instructions executed by the processor and backing out the higher-level intent of the human programmer. More specifically, decompiling is the process of generating source-level code from the executable object code

Decompiling is the process of generating source-level code from the executable object code embedded in a product's memory. It is a matter of reverse engineering the software.

embedded in a product's memory. It is a matter of reverse engineering the software.

Certainly the high-level intent of an application can be at least partially deduced by simply using the product. The user interface, system inputs and outputs, and general product behavior can be readily observed by any end user. Additionally, the architectures and instruction sets for commercial microprocessors are publicly available. Therefore, we can assume that someone who is familiar with your product and the microprocessor it uses already knows a good deal about your application, whether or not they have access to the software. This person is familiar with the processor's addressing modes, on-chip peripherals, address space, and so forth. So even though real-time interactions and algorithms are "hidden" in the object code, they can be recovered to some degree (maybe to a large degree) by decompiling the executable object code, which is often stored in a read-only memory (ROM) chip. This information could then be used to your competitive disadvantage.

What follows is a survey of possible techniques to discourage the would-be reverse engineer. Almost all of these techniques will only slow down the decompiling effort; they will not keep the reverse engineer from succeeding, given enough time, resources, and desire.

#### Methods of protection

Use a copyright notice in the binary file. This is certainly not a technical protection scheme—only a legal one. But including an ASCII copyright notice in the binary image at least notifies anyone reading the image that the software is legally protected and should not be tampered with. A copy-

right notice will not hinder an ethically challenged competitor or hacker, but it only takes up a handful of bytes in ROM, so little reason exists not to include it.

Use a checksum value over the whole application. This method allows you to detect modifications to the executable image. You'll need a boot program, which stores the correct checksum for your binary image. The boot program itself should reside in nonvolatile, protected memory, preferably inside of the microprocessor itself if it has onboard ROM of some type.

The boot program must also be able to calculate a checksum from the ROM image, and compare the result to the stored value. If the two values differ, the boot program inhibits execution of the application. This method offers no protection against reading and decompiling the code; it only protects against putting an altered ROM in the product and having the product still function.

Note that neither the boot program nor the stored checksum should be part of the ROM image that you're trying to protect. If the boot program can be located and decompiled, then this method offers no protection at all. That's why locating the boot program within the microprocessor itself is a good idea—the program is much more difficult to retrieve that way. Many of today's microcontrollers offer some on-board ROM or flash which can be used for this purpose. The checksum can be stored in EEPROM or flash.

Encrypt string data. If your product has any sort of human user interface, the software likely includes text strings. Compilers typically store the string data in ASCII format, and by default place this string data into constant data sections in the binary image.

Many binary file editors will display the ASCII interpretation of the raw hex data, so visually scanning the binary file and finding the address of each string is a simple matter. Once you know the addresses, you can search the executable code to see where they're used and draw some conclusions about what each section of code does.

One protection technique, then, is to encode text strings so they don't show up as readable ASCII in the binary image. (The encoding takes place outside of your application software, so that only the encoded representations appear in the binary image.) On a character-by-character basis, each character in the string can be mathematically manipulated in some way (for example, ANDing with a constant eight-bit "key") before being stored. The character must then be decoded before being sent to an output device. Or the encoding can take place on groups of characters.

In either case, you'll have to modify your language's output facilities, or perhaps write your own from scratch. In C, for instance, printf() has no inherent decryption capability, so you might choose to write your own version of printf() that knows how to turn an encoded string into legitimate ASCII data at run time.

If you are going to use string encryption, it's good practice to store critical information that is required to decode strings in the microprocessor's internal memory. For example, if you AND each character with an eight-bit key, the key should be stored within the microprocessor, so that it does not appear in the binary image anywhere.

Write your own operating system. If your application includes a commercial OS, certain "signatures" appear in

### Countless individual internet appliances.

| Imaging            | Internet Appliances | Internet Infrastructure |  |

|--------------------|---------------------|-------------------------|--|

| Telecommunications | Intelligent I/O     | Wireless                |  |

| Aerospace/Defense  | Automotive          | Industrial Control      |  |

### One common element.

In the booming market of Internet appliances, success is all about time-to market, cost and product differentiation. If you design to win in that environment, there's one company with whom you'll definitely see eye to eye — Wind River Systems.

With our Tornado embedded development tools and VxWorks real-time operating system, you'll have a huge head start in your product development cycle. Our open, reliable

architecture will allow you to differentiate your product for any sized design, all the way from the end-user application code to the look and feel of the graphical user interface.

By utilizing Wind River technology, Liberate Technologies (formerly known as NCI) rolled out its interactive TV software across Europe and the US, and TeraLogic, Inc. successfully launched its Cougar Reference Platform for HDTV. With over 200 Java design wins,

we've also made Java work in the embedded market. And our Universal Graphics Layer (UGL) provides a solid foundation for graphics development in the embedded space.

Find out more about Tornado and VxWorks. Visit www.wrs.com/html/espgene.html or call 1-800-545-WIND. Then give your designs the advantage of Wind River Systems. Because your competition is so fierce, you can't afford to blink first.

If the goal is to write well designed code for easier maintenance, then making poorly designed code in an attempt to protect it seems silly. However, critical algorithms may be obfuscated somewhat to hamper their decompilation and interpretation.

the binary image. The OS must include a start-up sequence, which is probably well documented by the OS vendor. Other run-time facilities will show up in the executable, and once these are found their interaction with your application code can be more quickly deciphered. And if the OS code is well designed and well coded, a decompiler program might have little trouble reconstructing the source code for OS functions.

If you use your own OS, a reverse engineer might need more time to figure out how your run-time environment works. However, writing your own run-time environment may not always be an option. Project schedules or legacy designs may dictate that you use a commercial OS. A home-grown kernel may only be a viable option for small, lower-memory projects that don't require accelerated design cycles.

Scramble address lines through extra logic. Another technique to hamper decompilation is to scramble address and/or data lines on your product's PC board(s). Instead of routing the address and data lines directly from the microprocessor to the ROM, you can insert some extra logic in between. An EPLD or FPGA can be a good source for such logic. So the address put out by the microprocessor, for example, will not be the physical ROM address to which an access is made. The ROM image will appear nonstandard, since the addresses have been essentially encoded. This fact alone might tip off a reverse engineer that something has been done to protect the code.

This method has other drawbacks, though. If your product can be instrumented with a logic analyzer, a reverse engineer can observe the "real" data being read by or written from the microprocessor. So while a decompiler may have a hard time with the ROM image, instruction sequences can still be determined at run time. In addition, you have the overhead of designing around the address/data line scrambling logic yourself, which may require you to have some type of special utility to create your ROM-able image, since linkers generally won't support this type of operation.

Replace library functions. This method follows the same philosophy as using your own kernel. Since programming languages have standard libraries of functions, you could choose to not use these functions and instead write your own. This would make searching for common functions, such as printf(), more difficult. But this adds a significant overhead to your design cycle, since you have to reinvent the wheel.

Write lousy code. This option may seem ridiculous, but in fact might slow down the potential reverse engineer. The more convoluted a software design is, the more difficult it is to figure out, even at the source-code level (especially if it is also poorly documented). I'm certain there are a myriad of ways that code can be made to be "lousy," and I won't begin to offer suggestions for writing lousy code here.

I'm not really suggesting that this is a viable protection scheme, since it flies in the face of every software methodology written. If the goal is to write well designed code for easier maintenance, then making poorly designed code in an attempt to protect it seems silly. However, critical algorithms may be obfuscated somewhat to hamper their decompilation and interpretation.

Implement critical algorithms in silicon. This is perhaps one of the most realistic options for product protection. If your application contains proprietary algorithms that are crucial to understanding how your product really works, implementing those algorithms in hardware rather than as code may be a good idea. Even if someone successfully decompiles your ROM, key pieces of the logic will be missing. For many applications, this may be enough protection to keep your product from being copied or modified.

Seal the electronics. The circuit board that includes your ROM could be encased in some sort of hard plastic sealant (potting or conformal coating) to make access to the device impossible. A would-be reverse engineer would have to physically destroy the product to get at the software. While this method may offer suitable protection against decompiling, it simultaneously presents a maintenance problem for you-the circuit board cannot be legitimately accessed to repair or replace the ROM and any other parts encased in sealant.

Use a home-grown microprocessor. If you have the time, resources, and need, designing your own microprocessor would provide a high level of protection against code decompilation. Assuming the architecture and instruction set for your processor are not publicly documented, the ROM image should be meaningless to anyone not familiar with your design. But this method is a large commitment, since you not only have to design the processor, you also have to create any compilers, assemblers, linkers, and debuggers to work with it.

However, an alternative does exist. Some microprocessor core companies provide licenses for their cores that include development tools to modify existing instructions, or add your own new instructions. The processor development tools allow you to generate a new core, plus they can generate a compiler for software development on your specialized processor. (Tensilica's Xtensa Processor Generator is one example of such a configurable processor environment.) As a result, you can create your own unique

# Rational Rose for real-time?

The result could be painful.

More and more development teams agree Real-time Studio™ is the better system and software modeling solution.

It makes perfect sense. If you're developing real-time embedded systems, you need a software modeling solution that can support your entire team and will actually fit your existing process. Make no mistake reach for Real-time Studio. This is the one and only software modeling solution with an object-based repository enabling complete, up-to-date, shared views of your system. Finally, your entire development team can communicate and collaborate — from start to product delivery. Developed exclusively for real-time systems, Real-time Studio is non-intrusive, flexible and features automatic code generation for C, C++, and Java. Today, it's the proven solution for hundreds of developers and development teams. And the list keeps growing. Get started on the fastest path to the right product. Visit www.artisansw.com/real for more information and a demo of Real-time Studio, plus you can register for our upcoming Real-time UML seminar.

Real-time Studio<sup>™</sup> www.artisansw.com/real

No developer was actually harmed or risked injury in the making of this ad. Rational Rose is a registered trademark of Rational Software Corporation. Real-time Studio is a trademark of Artisan Software Tools, Inc.

Even if a hacker were willing to physically damage a unit to gain access to the binary executable, he would be unable to modify the code and still use the unit to obtain service.

instructions to implement critical algorithms which need special protection. Burn an FPGA with your modified core and you have a working prototype for software development. The final microprocessor can then be fabricated as an ASIC.

#### Two scenarios

Let's discuss two basic scenarios that might warrant the protection of a binary executable. In the first scenario, we must keep someone from modifying the code in a particular device so that features cannot be overridden or circumvented. Preventing this person from decompiling and understanding the code isn't necessary; rather, we're interested only in preventing modification of the executable. In the second scenario, we do need to thwart decompilation, to protect intellectual property rights in a competitive environment.

The first scenario is exemplified by various communications services, such as cable and satellite television or the caller ID telephone feature. In both cases the service provider supplies a customer with special equipment. In the cable TV case, the customer needs a cable TV converter box; with caller ID, the customer needs a display unit which indicates who is calling. The service provider often charges relatively little for the hardware itself, since it isn't the hardware that generates longterm revenue. The hardware simply serves as a gateway for a customer to access information (the cable program or the caller ID), and it is this information for which the customer must pay.

In these two cases, we are interested in protecting the firmware running in the customer's hardware from being altered in a way that enables the customer to get access to the service without paying for it. But it isn't necessarily important to keep someone from decompiling the software to understand how it works-no revenue will be lost unless the software is modified in an attempt to circumvent billing.

The manufacturer of the cable converter or caller ID unit could employ the checksum technique to ensure that the embedded software cannot be altered and still operate. If packaging limitations allow, the electronics could be encased in sealant to make access to the ROM difficult or impossible without destroying the unit. Better yet, both methods can be used at the same time to offer increased protection. Even if a hacker were willing to physically damage a unit to gain access to the binary executable, he would be unable to modify the code and still use the unit to obtain service.

The second scenario leans more toward the protection of intellectual property and the threat of bona fide competition in the marketplace, not just casual hacking. Any product, particularly those that are cutting-edge in their specific industries, can be a target of reverse engineering by an unethical competitor. In these cases it may be worth the cost to implement some of the more aggressive protection techniques listed in the survey. In particular, the home-grown microprocessor technique may prove to be a viable option.

Consider a hypothetical example: let's say your company has developed a new type of portable medical diagnostic device that allows patients to monitor some aspect of their own health in real time (this is a hypothetical example, remember). Your company is pursuing a patent on the technology, but you need to get the device to market as quickly as possible. In this case, especially if the potential market is large, you may decide to modify an

existing processor core to hide key aspects of your algorithms. In this way potential competitors will not be able to unlock the secrets of your application unless they first get information about your specialized processor and the instruction set it uses.

#### Weighing the costs

The code protection techniques that aren't too costly to implement can be somewhat readily overcome by competitors, while those techniques that are more iron-clad may require a substantial investment. It may be that the cost to implement such an iron-clad method overwhelms the "normal" cost of development for the product. The bottom line is, if someone is willing to spend the time and money, little can be done to stop reverse engineering of embedded code. Even if you use custom hardware, there are clever engineers who understand a commercially available CPU well enough to make logical (and often correct) assumptions about the details of your design.

A custom microprocessor with an unpublished instruction set, or physically sealing the electronics in some manner, might satisfactorily protect the software, but these may not be viable solutions for many applications (particularly in smaller organizations with smaller development budgets). Ultimately, the decision of whether or not to put protection schemes in place may in fact be a business decision and not a purely technical one. The company must weigh the cost of implementing code protection vs. the potential risk of intellectual property infringements or loss of service revenue, and decide what is best for its particular situation.

Matt Fisher is a software engineer who has been working with embedded systems for the past five years. He has experience in the defense, telecommunications, and electronics industries, and holds a BS and MEng in electrical engineering from Rensselaer Polytechnic Institute in Troy, NY. He can be reached at matt\_fisher@ieee.org.

- **Operating Systems**

- Bundled Toolsets

- **Design Services**

- Consulting

Phone: I-877-983-4514

For more information please visit: www.blackhawk-dsp.com

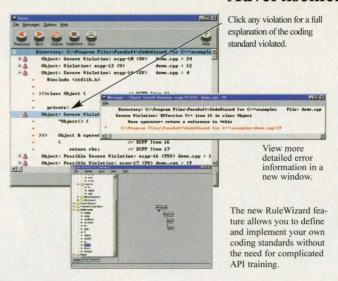

#### **Unit Testing Prevents Errors**

#### by Adam Kolawa

In previous columns, we have focused on coding standards as a type of error prevention. This month we shall introduce unit testing, which is another important facet of the error prevention process. To understand the importance of unit testing, we must first take a look at the current state of software testing.

Developers today face increasing deadline pressure as they write code in a competitive software market. They often write code quickly and send it off to another department for testing. However, the best person to test code is the developer who wrote it. He or she understands the code better than anyone else and is most capable of finding the weaknesses in the code.

As developers test code, they should not just be trying to finish quickly and go home early. Rather, they should be trying to break the code in any way possible. Instead of mentally rewarding yourself for code that appears clean, you should reward yourself for finding bugs. Adopt a new, more critical outlook on your code, and you will see dividends in the cleanliness of that code.

Once you have adopted this new outlook, you need to find an effective method of testing. Unit testing is one of the most effective methods available.

Developers often hear about unit testing and think the term refers to module testing. But unit testing actually refers to an even lower level of testing that occurs at the class or object level. Class-level testing is extremely important to the well-being of any application. However, most developers avoid class testing and believe that it is not possible to perform on large applications because of the labor and techniques involved.

In upcoming columns, we shall illustrate that although manual unit testing at the class level involves some extra work, the technique is certainly feasible and worthwhile. Furthermore, technology has evolved to the point that developers can now choose from a number of powerful tools that make unit testing as easy as breathing.

Dr. Adam Kolawa is President and CEO of ParaSoft. You can reach him by e-mail at ukola@parasoft.com.

#### Advertisement

# **Would you believe** that CodeWizard®can prevent errors in your code and cut your debugging by 25%?

"CodeWizard is the code reviewer without the attitude; it knows all the rules." -- Suzette LaGray Siemens ElectroCom L.P.

CodeWizard® is a tool that helps you prevent errors by automatically performing static analysis on C++ code. The first thing you need to know about CodeWizard is that it can help you do less of the thing you hate the most: debugging. With CodeWizard, preventing errors before they happen is painless.

CodeWizard automatically enforces over 70 C++ coding standards, which are language-specific rules that help you to avoid dangerous coding constructs. The standards are borrowed from the writings of Scott Meyers and other industry experts. CodeWizard clearly displays each of your violations and gives you all the information you need to fix them, including suggestions on better coding constructs. No more wondering about weaknesses in your code. Follow CodeWizard's coding suggestions, and you'll immediately begin to write cleaner, more reliable code.

The key to CodeWizard is that you can configure the program to avoid overworking yourself. With a few clicks, you can tell CodeWizard to enforce only the standards that are most relevant to the current project. Using the new RuleWizard™ feature, you can even write your own coding standards with point-and-click convenience. Use CodeWizard and RuleWizard together, and you'll have a personalized tool for your entire development team. This is a tool that conforms to you–not the other way around.